在当今数据爆炸的时代,传统基于冯·诺依曼架构的计算系统正面临日益严峻的挑战。该架构将计算单元(CPU/GPU)与存储单元(内存)物理分离,数据需要在两者之间频繁搬运,导致巨大的功耗开销和性能瓶颈,即所谓的“内存墙”问题。存算一体技术应运而生,它通过将计算功能直接嵌入到存储单元内部或附近,实现了数据处理与存储的深度融合,为突破传统计算范式提供了革命性的解决方案。

一、存算一体的硬件架构创新

存算一体的核心在于硬件层面的根本性重构。它并非简单地将处理器和存储器放在同一芯片上,而是旨在消除或大幅减少数据移动。主要技术路径包括:

- 基于新型非易失存储器的存内计算:利用忆阻器、相变存储器、磁性存储器等器件的物理特性(如电阻值)直接表示和处理数据。这些器件既能存储信息,又能通过模拟或数字方式进行逻辑运算或向量矩阵乘法,尤其适合人工智能中常见的乘累加计算。

- 近存计算:通过先进的封装技术(如2.5D/3D集成),将计算逻辑单元与高带宽存储器紧密堆叠在一起,显著缩短互连距离,提供极高的内存访问带宽,从而缓解数据搬运压力。

- 存内逻辑:直接在存储阵列中利用存储单元本身或外围电路实现布尔逻辑运算,使数据在原地即可被处理。

这些架构创新从根本上改变了数据流,将“数据移动计算”转变为“计算移向数据”,从而大幅提升能效比和计算吞吐量。

二、算法与架构的协同优化

硬件架构的革新必须与算法设计深度协同,才能最大化存算一体的潜力。这体现在:

- 算法映射与适配:传统算法通常为冯·诺依曼架构设计。存算一体架构,尤其是模拟存内计算,需要将算法(如神经网络模型)高效地映射到非理想的物理器件阵列上。这涉及到权重量化、精度容忍、数据流重构等适配工作。

- 利用计算范式特性:存算一体天然适合数据并行和空间计算范式。算法设计应充分利用其大规模并行执行矩阵向量运算的能力,优化数据布局和任务调度,以匹配硬件的并行粒度。

- 软硬件协同设计:从算法设计初期就考虑底层硬件的约束与优势,进行联合优化。例如,设计对器件非理想性(如工艺偏差、噪声)鲁棒的算法,或开发新的稀疏化、压缩算法来匹配存算阵列的结构。

三、数据处理与存储支持服务的演进

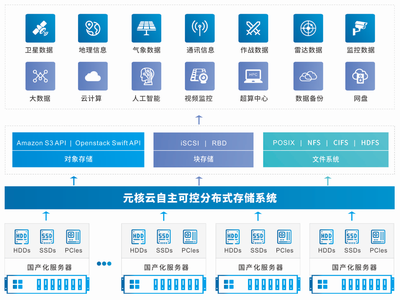

存算一体技术的落地,将深刻改变整个数据处理和存储服务栈:

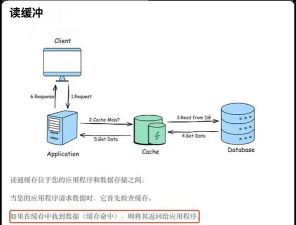

- 新型存储层次与数据管理:存算一体芯片可能成为介于传统内存和存储之间的新层次。操作系统和运行时系统需要管理这种既能存又能算的资源,发展新的数据放置策略、缓存机制和一致性模型。

- 异构计算生态的支持:存算一体加速器将作为异构计算系统的重要组成部分。需要完善的编译器、编程模型、驱动和库支持,让开发者能够高效利用其计算能力,例如开发专用的领域特定语言或扩展现有框架。

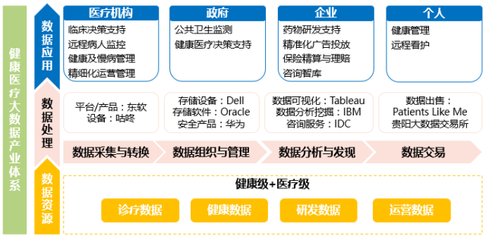

- 面向场景的解决方案:存算一体技术并非通用万能,其优势场景突出体现在数据密集型应用上,如:

- 边缘AI与物联网:极低的功耗使其非常适合设备端实时智能处理。

- 大数据分析:加速数据库查询、图计算等内存受限操作。

* 高性能计算:加速科学计算中的稀疏线性代数运算。

相应的数据处理服务需要针对这些场景进行定制和优化。

四、挑战与展望

尽管前景广阔,存算一体技术走向大规模商用仍面临挑战:器件精度与一致性、制造工艺、系统集成复杂度、生态建设等。未来发展需要材料、器件、电路、架构、算法、软件等多个层面的持续突破与协同创新。

总而言之,存算一体技术通过硬件架构与算法的协同优化,正引领一场突破冯·诺依曼瓶颈的深刻变革。它不仅是一种新的芯片技术,更将催生全新的数据处理范式和服务模式,为人工智能、物联网、大数据等关键领域注入强劲动力,推动计算技术进入一个更高效、更智能的新时代。